### DATA SHEET

# M3202A PXIe Arbitrary Waveform Generator with Optional Real-Time Sequencing and FPGA Programming 1 GSa/s, 14 Bits, 4 Channels

### Generate High-Precision, Complex, Real-World Signals

The M3202A high-performance, high-bandwidth arbitrary waveform generator combines an advanced waveform generation system with embedded function generators and modulators (frequency/phase/amplitude) for broadband and IF signal generation. Performance meets simplicity thanks to easy-to-use programming libraries, real-time sequencing technology (Hard Virtual Instrumentation or HVI technology), and graphical FPGA programming technology.

#### Features

- 1 GS/s, 14 bits, 4 ch, 400 MHz BW (800 MHz IQ)

- Embedded advanced arbitrary waveform generators (AWGs)

- Advanced triggering and marking (up to 8 reconfigurable I/Os)

- Waveform queue system with cycles, delays and prescalers

- Embedded high-precision function generators (FGs)

- Sinusoidal, triangular, square, DC, and more

- 45-bit frequency resolution (up to ~ 5.68 μHz)

- 24-bit phase resolution (up to ~ 21.5 µdeg)

- Embedded ultra-flexible amplitude and angle modulators

- High-quality output signal with low phase noise

- SFDR: ~ 54 dBc @ 160 MHz

- Average noise density: down to ~ -145 dBm/Hz

- Optional features

- Simultaneous amplitude and angle modulations

- Up to 2 GB of onboard RAM (~ 1 Gsamples)

- Mechanical/interface

- 1 slot 3U (PXIe)

- PCle Gen1

- $\circ$   $\,$  Independent direct memory access (DMA) channels for fast and efficient data transfer  $\,$

#### Applications

Quantum computing, 5G research

Manufacturing in wireless devices, automated test equipment (ATE)

MIMO, beam forming and other multi-channel coherent signal generation

General purpose, RF/arbitrary waveform generation

R&D/scientific research equipment, aerospace and defense (A/D)

# Programming Technology and Software Tools

### Software programming

• Easy-to-use native programming libraries for most common languages: C, C++, Visual Studio, LabVIEW, MATLAB, and Python

#### Hardware programming (optional)

- Real-time sequencing (Hard Virtual Instrumentation or HVI technology)

- Ultra-fast, fully-parallelized, hard real-time execution

- Ultra-fast, time-deterministic decision-making

- o Off-the-shelf inter-module synchronization and data exchange

- FPGA programming

- FPGA design environment and BSP support

- Supports VHDL, Verilog and Xilinx projects, and Xilinx IP Catalog

- o Ultra-fast, one-click compiling and on-the-fly programming

#### SD1 2.x and SD1 3.x differences

Keysight SD1 2.x software has been upgraded to 3.x. The key differences are listed in the table below. For more detail on SD1 3.x software, refer to the Start Up Guide M3xxx-90002.

#### WARNING

The 3.X version of software does not support programs using the M3601A or the M3602A applications. You will have to transition to KS2201A and KF9000A respectively.

| SD1 software features | Legacy (SD1 2.1.x)                             | New (SD1 3.x)                                                                            |  |  |  |  |  |  |  |

|-----------------------|------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Software              |                                                |                                                                                          |  |  |  |  |  |  |  |

|                       | M3601A HVI design environment<br>(ProcessFlow) | KS2201A PathWave Test Sync<br>Executive (HVI2 technology)                                |  |  |  |  |  |  |  |

| Design Environment    | M3602A FPGA design<br>environment (FPGAFlow)   | KF9000A PathWave FPGA<br>Programming Environment<br>(commonly known as PathWave<br>FPGA) |  |  |  |  |  |  |  |

|                       | Graphical M3601A for HV1                       | KS2201A PathWave Test Sync                                                               |  |  |  |  |  |  |  |

| HVI Technology        | HVI-C API (through SD1 installer)              | Executive (HVI2 Core API through a separate HVI installer)                               |  |  |  |  |  |  |  |

|                       | Graphical M3602A                               | KF9000A PathWave FPGA (BSP                                                               |  |  |  |  |  |  |  |

| FPGA Programming      | PathWave FPGA (BSP for SD1 2.1.x only)         | installer for each supported module is required)                                         |  |  |  |  |  |  |  |

| SD1 software features                                                                  | Legacy (SD1 2.1.x)                                                                | New (SD1 3.x)                                                                |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Software                                                                               |                                                                                   |                                                                              |  |  |  |  |  |  |  |

| Soft Front Panel (SFP)                                                                 | Available                                                                         | Available                                                                    |  |  |  |  |  |  |  |

| Programming Interface                                                                  | Python <sup>1</sup> , C++, C#, LabVIEW, MATLAB                                    | Python <sup>1</sup> , C, C++, C#, LabVIEW, MATLAB                            |  |  |  |  |  |  |  |

| Supported Operating<br>System                                                          | Windows 10 (32 / 64 bit)                                                          | Windows 10 (64 bit)                                                          |  |  |  |  |  |  |  |

|                                                                                        | Hardware modules                                                                  |                                                                              |  |  |  |  |  |  |  |

| M3202A (AWG 1G)                                                                        | FW version < 4.0 (CH4) (CLF)<br>(K16, K32, K41)                                   | FW version > =4.0 (CH4) (CLF /<br>CLV**) (K16, K32, K41)                     |  |  |  |  |  |  |  |

|                                                                                        | BSP available (K32, K41)                                                          | BSP available (K32, K41)                                                     |  |  |  |  |  |  |  |

| M3201A (AWG 500)                                                                       | FW version < 4.0 (CH4) (CLF)<br>(K16, K32, K41)                                   | FW version > =4.0 (CH4) (CLF /<br>CLV**) (K16, K32, K41)                     |  |  |  |  |  |  |  |

|                                                                                        | BSP available (K32, K41)                                                          | BSP available (K32, K41)                                                     |  |  |  |  |  |  |  |

| M3102A (DIG 500)                                                                       | FW version < 2.0 (CH4) (CLF)<br>(K16, K32, K41)                                   | FW version > =2.0 (CH4) (CLF)<br>(K16, K32, K41)                             |  |  |  |  |  |  |  |

|                                                                                        | BSP available (K32, K41)                                                          | BSP available (K32, K41)                                                     |  |  |  |  |  |  |  |

| M3100A (DIG 100)                                                                       | FW version < 2.0 (CH4 or CH8)<br>(CLF) (K16, K32, K41)                            | FW version > =2.0 (CH4 or CH8)<br>(CLF) (K32, K41)                           |  |  |  |  |  |  |  |

|                                                                                        | BSP available (K32, K41)                                                          | BSP available (K32, K41)                                                     |  |  |  |  |  |  |  |

| M3302A                                                                                 | FW version < 4.0 (CH2 AWG -<br>CH2 DIG) (CLF) (K32*, K41)                         | FW version > =4.0 (CH2 AWG -<br>CH2 DIG) (CLF) (K41)                         |  |  |  |  |  |  |  |

| (COMBO 500 500)                                                                        | BSP available (K32*, K41)                                                         | BSP available (K41)                                                          |  |  |  |  |  |  |  |

| M3300A<br>(COMBO 500 100)                                                              | FW version < 4.0 (CH2 AWG -<br>CH4 DIG or CH4 AWG - CH8<br>DIG) (CLF) (K32*, K41) | FW version > =4.0 (CH2 AWG -<br>CH4 DIG or CH4 AWG - CH8 DIG)<br>(CLF) (K41) |  |  |  |  |  |  |  |

|                                                                                        | BSP available (K32*)                                                              | BSP available (K41)                                                          |  |  |  |  |  |  |  |

| No programming                                                                         |                                                                                   |                                                                              |  |  |  |  |  |  |  |

| Easily configurable SD1 SFP (software front panel) interface for each connected module |                                                                                   |                                                                              |  |  |  |  |  |  |  |

1. HVI programming is supported with Python version 3.7 only.

\* This Hardware Option cannot be procured. Contact Keysight Support for more information.

\*\* Only Default Clock Speed is supported. Variable Clock is NOT Supported.

|         |           |                  | Outputs |     | Inputs (Digitizers) |                  |      |        |          |

|---------|-----------|------------------|---------|-----|---------------------|------------------|------|--------|----------|

| Product | Туре      | Speed<br>(MSa/s) | Bits    | Ch  | BW (MHz)            | Speed<br>(MSa/s) | Bits | Ch     | BW (MHz) |

| M3202A  | AWG       | 1000             | 14      | 4   | DC-400              |                  |      |        |          |

| M3201A  | AWG       | 500              | 16      | 4   | DC-200              |                  |      |        |          |

| M3102A  | Digitizer |                  |         |     |                     | 500              | 14   | 4      | DC-200   |

| M3100A  | Digitizer |                  |         |     | 100                 | 14               | 4/8  | DC-100 |          |

| M3302A  | Combo     | 500              | 16      | 2   | DC-200              | 500              | 14   | 2      | DC-200   |

| M3300A  | Combo     | 500              | 16      | 2/4 | DC-200              | 100              | 14   | 4/8    | DC-100   |

### PXIe Arbitrary Waveform Generators, Digitizers and Combination Modules

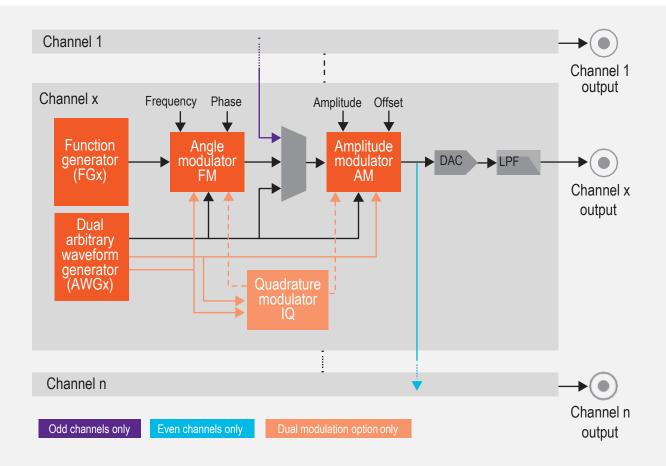

### Functional Block Diagram

Figure 1. M3201A output functional block diagram, all channels have identical output structure

# Ordering Information<sup>1</sup>

| Product                                     | Description                                                                                     |

|---------------------------------------------|-------------------------------------------------------------------------------------------------|

| M3202A                                      | PXI arbitrary waveform generator: 1 GSa/s, 14 Bits                                              |

| Options                                     | Description                                                                                     |

| M3202A-CH4 <sup>2</sup>                     | Four channels                                                                                   |

| M3202A-CLF <sup>2</sup> / -CLV <sup>4</sup> | Fixed / Variable sampling clock, low jitter                                                     |

| M3202A-DM1                                  | Dual modulation capability (amplitude and angle simultaneously)                                 |

| M3202A-M01 <sup>2</sup> / -M12 / -M20       | Memory 16 MB, 8 MSamples / 128 MB, 60 MSamples / 2 GB, 1 GSamples                               |

| Options                                     | Description                                                                                     |

| M3202A-HVI                                  | Enables HVI programming, requires the -HV1 option and the HVI software license (KS2201A)        |

| M3202A-FP1                                  | Enables FPGA programming, requires -K41 option and an FPGA design environment license (KF9000A) |

| M3202A-K32 / K41                            | FPGA, Xilinx 7K325T / 7K410T, required for -FP1 option only (needs memory option -M20)          |

| Options <sup>3</sup>                        | Description                                                                                     |

| M3601A                                      | HVI design environment                                                                          |

| M3602A                                      | FPGA design environment                                                                         |

| KS2201A                                     | PathWave Test Sync Executive                                                                    |

| KF9000A                                     | Pathwave FPGA                                                                                   |

All options must be selected at time of purchase and are not upgradable.

These options represent the standard configuration.

M3601A / M3602A are supported with SD1 2.x software only whereas KS2201A / KF9000A are supported with SD1 3.x software only.

4. Only the option CLF is supported. The option CLV is not supported.

# **Technical Specifications and Characteristics**

General characteristics

| Devenue (ev                      | M3202A-CH4 |          | Units     | <b>0</b> |                              |

|----------------------------------|------------|----------|-----------|----------|------------------------------|

| Parameter                        | Min        | Тур      | Max       | Units    | Comments                     |

|                                  |            | Input    | ts and ou | Itputs   |                              |

| Channels (single-ended mode)     |            | 4        |           | Out      |                              |

| Channels (differential mode)     |            | 2        |           | Out      | Differential uses 2 channels |

| Reference clock <sup>1</sup>     |            | 1        |           | Out      |                              |

| Reference clock <sup>2</sup>     |            | 1        |           | In       |                              |

| Triggers/markers <sup>1, 3</sup> |            | 1        |           | In/out   | Reconfigurable               |

| Triggers/markers <sup>2,3</sup>  |            | 8        |           | In/out   | Reconfigurable               |

|                                  |            | Output o | hannels   | overview |                              |

| Sampling rate                    |            | 1000     |           | MSa/s    |                              |

| Voltage resolution               |            | 14       |           | Bits     |                              |

| Output frequency                 | DC         |          | 400       | MHz      |                              |

| Real-time BW                     |            | 400      |           | MHz      |                              |

| Output voltage                   | -1.5       |          | 1.5       | Volts    |                              |

|                                  |            | Built-i  | n functio | nalities |                              |

| Function generators              |            | 4        |           |          | 1 per channel                |

| Dual AWGs                        |            | 4        |           |          | 1 per channel                |

| IQ modulators                    |            | 4        |           |          | 1 per channel                |

| Frequency modulators             |            | 4        |           |          | 1 per channel                |

| Phase modulators                 |            | 4        |           |          | 1 per channel                |

| Amplitude modulators             |            | 4        |           |          | 1 per channel                |

| DC offset modulators             |            | 4        |           |          | 1 per channel                |

|                                  |            | Onb      | oard mei  | mory     |                              |

| RAM memory                       | 16         |          | 2048      | MBytes   |                              |

At front panel.

At backplane.

Markers available from SD1 software version v3.0 or later.

# I/O specifications

| Demonster        | M    | 3202A-CH     | 14        | 11.5%            | 0                                                  |  |  |  |

|------------------|------|--------------|-----------|------------------|----------------------------------------------------|--|--|--|

| Parameter        | Min  | Тур          | Max       | Units            | Comments                                           |  |  |  |

| Output channels  |      |              |           |                  |                                                    |  |  |  |

| Sampling rate    | 1.0  |              |           | GSa/s            |                                                    |  |  |  |

| Output frequency | DC   |              | 400       | MHz              | Limited by a reconstruction filter                 |  |  |  |

| Output voltage   | -1.5 |              | 1.5       | Vp               | On a 50 Ω load                                     |  |  |  |

| Source impedance | 50   |              |           | Ω                |                                                    |  |  |  |

|                  |      | Refere       | nce clock | output           |                                                    |  |  |  |

| Frequency        |      | 10 or<br>100 |           | MHz              | Generated from the internal clock, user selectable |  |  |  |

| Voltage          |      | 800          |           | mV <sub>pp</sub> | On a 50 Ω load                                     |  |  |  |

| Power            |      | 2            |           | dBm              | On a 50 Ω load                                     |  |  |  |

| Source impedance |      | 50           |           | Ω                | AC coupled                                         |  |  |  |

|                  |      | External     | I/O trigg | er/marker        |                                                    |  |  |  |

| Vih              | 2    |              | 5         | V                |                                                    |  |  |  |

| VIL              | 0    |              | 0.8       | V                |                                                    |  |  |  |

| Vон              | 2.4  |              | 3.3       | V                | On a high Z load                                   |  |  |  |

| Vol              | 0    |              | 0.5       | V                | On a high Z load                                   |  |  |  |

| Input impedance  |      | 10           |           | KΩ               |                                                    |  |  |  |

| Source impedance |      | TTL          |           | -                |                                                    |  |  |  |

| Speed            |      | 100          |           | MHz              |                                                    |  |  |  |

# Function generators (FGs) specifications

| Devenator                 | N                     | 13202A-CH | 14        | Units      | Commente                              |

|---------------------------|-----------------------|-----------|-----------|------------|---------------------------------------|

| Parameter                 | Parameter Min Typ Max |           | Units     | Comments   |                                       |

|                           |                       | Gener     | ral speci | fications  |                                       |

| Function generators       |                       | 4         |           | _          | 1 per channel                         |

| Waveform types            |                       | 4         |           | _          | Sinusoidal, triangular, square and DC |

| Frequency range           | 0                     |           | 400       | MHz        |                                       |

| Frequency resolution      |                       | 45        |           | Bits       |                                       |

| Frequency resolution      |                       | 11.4      |           | μHz        |                                       |

| Phase range               | 0                     |           | 360       | Deg        |                                       |

| Phase resolution          |                       | 24        |           | Bits       |                                       |

| Phase resolution          |                       | 21.5      |           | µdeg       |                                       |

|                           |                       | Spee      | ed perfo  | rmance     |                                       |

| Frequency change rate     |                       | 100       |           | MChanges/s | With HVI technology                   |

| Frequency modulation rate |                       | 1000      |           | MSamples/s | With AWGs and angle modulators        |

| Phase change rate         |                       | 100       |           | MChanges/s | With HVI technology                   |

| Phase modulation rate     |                       | 1000      |           | MSamples/s | With AWGs and angle modulators        |

# Amplitude and offset specifications

| Deverseter                         | N    | 13202A-CH | 4        | Units      | Commente                           |  |  |  |

|------------------------------------|------|-----------|----------|------------|------------------------------------|--|--|--|

| Parameter                          | Min  | Тур       | Max      | Units      | Comments                           |  |  |  |

| General specifications             |      |           |          |            |                                    |  |  |  |

| Amplitude / offset range           | -1.5 |           | 1.5      | Vp         | Amplitude + offset values          |  |  |  |

| Amplitude / offset resolution      |      | 14        |          | Bits       |                                    |  |  |  |

| Amplitude / offset resolution      |      | 183.1     |          | μV         |                                    |  |  |  |

|                                    |      | Spee      | ed perfo | rmance     |                                    |  |  |  |

| Amplitude / offset change rate     |      | 1000      |          | MChanges/s | With HVI technology                |  |  |  |

| Amplitude / offset modulation rate |      | 1000      |          | MSamples/s | With AWGs and amplitude modulators |  |  |  |

# Arbitrary waveform generators (AWGs) specifications

|                              | M3202A-CH4 |             | 14         | 11.14            |                                                                        |  |

|------------------------------|------------|-------------|------------|------------------|------------------------------------------------------------------------|--|

| Parameter                    | Min        | Тур         | Max        | Units            | Comments                                                               |  |

|                              |            | Genera      | l specifi  | cations          |                                                                        |  |

| Dual AWGs                    |            | 4           |            |                  | 1 dual AWG per output channel                                          |  |

| Aggregated speed (16 bits)   |            |             | 4          | GSa/s            | For all onboard waveforms combined                                     |  |

| Aggregated speed (32 bits)   |            |             | 2          | GSa/s            | For all onboard waveforms combined                                     |  |

| Waveform multiple            |            | 5           |            | Samples          | Waveform length must be a multiple of this value                       |  |

| 16-bit waveform length       | 65         |             | 957        | MSamples         | Maximum depends on onboard RAM                                         |  |

| 32-bit waveform length       | 65         |             | 478        | MSamples         | Maximum depends on onboard RAM                                         |  |

| Waveform length efficiency   |            | 93.5        |            | %                | Efficiency = waveform size /<br>waveform size in RAM                   |  |

| Trigger                      |            | Select      |            |                  | External trigger (input connector, backplane triggers), SW/HVI trigger |  |

|                              | AWG sp     | ecification | is (16-bit | single wavefor   | m)                                                                     |  |

| Speed                        |            |             | 1          | GSa/s            | Per AWG                                                                |  |

| Resolution                   |            | 16          |            | Bits             |                                                                        |  |

| AWG destination              |            | Select      |            |                  | Amplitude, offset, frequency or phase                                  |  |

|                              | AWG s      | pecificatio | ns (16-b   | it dual waveforr | n)                                                                     |  |

| Speed (waveform A)           |            |             | 1          | GSa/s            | Per AWG                                                                |  |

| Speed (waveform B)           |            |             | 1          | GSa/s            | Per AWG                                                                |  |

| Resolution (waveform A)      |            | 16          |            | Bits             |                                                                        |  |

| Resolution (waveform B)      |            | 16          |            | Bits             |                                                                        |  |

| AWG destination (waveform A) |            | Select      |            |                  | Amplitude and offset or I and Q control outputs on channels            |  |

| AWG destination (waveform B) |            | Select      |            |                  | Frequency and phase or I and Q readouts on channels                    |  |

|                              | AWG sp     | ecification | is (32-bit | single wavefor   | m)                                                                     |  |

| Speed                        |            |             | 0.1        | GSa/s            | Per AWG, minimum prescaler: 1                                          |  |

| Resolution                   |            | 32          |            | Bits             |                                                                        |  |

| AWG destination              |            | Select      |            |                  | Amplitude, offset, frequency or phase                                  |  |

| Speed (waveform A)           |            |             | 0.1        | GSa/s            | Per AWG, minimum prescaler: 1                                          |  |

| Speed (waveform B)           |            |             | 0.1        | GSa/s            | Per AWG, minimum prescaler: 1                                          |  |

| Resolution (waveform A)      |            | 32          |            | Bits             |                                                                        |  |

| Resolution (waveform B)      |            | 32          |            | Bits             |                                                                        |  |

| AWG destination (waveform A) |            | Select      |            |                  | Amplitude or offset                                                    |  |

| AWG destination (waveform B) |            | Select      |            |                  | Frequency or phase                                                     |  |

# Angle modulators specifications

|                              | N             | /I3202A-CH   | 4                | 11.96    |                                                             |  |  |  |  |

|------------------------------|---------------|--------------|------------------|----------|-------------------------------------------------------------|--|--|--|--|

| Parameter                    | Min           | Тур          | Мах              | Units    | Comments                                                    |  |  |  |  |

| General specifications       |               |              |                  |          |                                                             |  |  |  |  |

| Frequency modulators         |               | 4            |                  |          | 1 per output channel                                        |  |  |  |  |

| Phase modulators             |               | 4            |                  |          | 1 per output channel                                        |  |  |  |  |

| Carrier signal source        |               | FGs          |                  |          | Refer to the FG<br>specifications table in this<br>document |  |  |  |  |

| Modulating signal source     |               | AWGs         |                  |          | Refer to the AWG specifications table in this document      |  |  |  |  |

| F                            | requency modu | lators (16-b | oit modulating w | aveform) |                                                             |  |  |  |  |

| Deviation                    | –Dev. gain    |              | +Dev. gain       | MHz      |                                                             |  |  |  |  |

| Modulating signal resolution |               | 16           |                  | Bits     | AWG waveform                                                |  |  |  |  |

| Modulating signal BW         | 0             |              | 500              | MHz      | AWG Nyquist limit                                           |  |  |  |  |

| Deviation gain               | 0             |              | 400              | MHz      |                                                             |  |  |  |  |

| Deviation gain resolution    |               | 16           |                  | Bits     |                                                             |  |  |  |  |

| F                            | requency modu | lators (32-b | oit modulating w | aveform) |                                                             |  |  |  |  |

| Deviation                    | –Dev. gain    |              | +Dev. gain       | MHz      |                                                             |  |  |  |  |

| Modulating signal resolution |               | 32           |                  | Bits     | AWG waveform                                                |  |  |  |  |

| Modulating signal BW         | 0             |              | 100              | MHz      | AWG Nyquist limit                                           |  |  |  |  |

| Deviation gain               | 0             |              | 400              | MHz      |                                                             |  |  |  |  |

| Deviation gain resolution    |               | 16           |                  | Bits     |                                                             |  |  |  |  |

|                              | Phase modulat | ors (16-bit  | modulating wav   | eform)   |                                                             |  |  |  |  |

| Deviation                    | –Dev. gain    |              | +Dev. gain       | Deg      |                                                             |  |  |  |  |

| Modulating signal resolution |               | 16           |                  | Bits     | AWG waveform                                                |  |  |  |  |

| Modulating signal BW         | 0             |              | 500              | MHz      | AWG Nyquist limit                                           |  |  |  |  |

| Deviation gain               | 0             |              | 180              | Deg      |                                                             |  |  |  |  |

| Deviation gain resolution    |               | 16           |                  | Bits     | ~ 5.5 mdeg                                                  |  |  |  |  |

|                              | Phase modulat | ors (32-bit  | modulating wav   | eform)   |                                                             |  |  |  |  |

| Deviation                    | –Dev. gain    |              | +Dev. gain       | Deg      |                                                             |  |  |  |  |

| Modulating signal resolution |               | 16           |                  | Bits     | AWG waveform is truncated                                   |  |  |  |  |

| Modulating signal BW         | 0             |              | 100              | MHz      | AWG Nyquist limit                                           |  |  |  |  |

| Deviation gain               | 0             |              | 180              | Deg      |                                                             |  |  |  |  |

| Deviation gain resolution    |               | 16           |                  | Bits     | ~ 5.5 mdeg                                                  |  |  |  |  |

# Amplitude modulators specifications

| Demonster                                                    |               | M3202A-CH4  |                  | 11.5%     | <b>O</b>                                               |  |  |  |  |  |

|--------------------------------------------------------------|---------------|-------------|------------------|-----------|--------------------------------------------------------|--|--|--|--|--|

| Parameter                                                    | Min           | Тур         | Max              | Units     | Comments                                               |  |  |  |  |  |

| General specifications                                       |               |             |                  |           |                                                        |  |  |  |  |  |

| Amplitude modulators                                         |               | 4           |                  |           | 1 per output channel                                   |  |  |  |  |  |

| Offset modulators                                            |               | 4           |                  |           | 1 per output channel                                   |  |  |  |  |  |

| Carrier signal source                                        |               | FGs         |                  |           | Refer to the FG specifications table in this document  |  |  |  |  |  |

| Modulating signal source                                     |               | AWGs        |                  |           | Refer to the AWG specifications table in this document |  |  |  |  |  |

| Amplitude and offset modulators (16-bit modulating waveform) |               |             |                  |           |                                                        |  |  |  |  |  |

| Deviation                                                    | -Dev. gain    |             | +Dev. gain       | Vp        |                                                        |  |  |  |  |  |

| Modulating signal resolution                                 |               | 16          |                  | Bits      | AWG waveform                                           |  |  |  |  |  |

| Modulating signal BW                                         | 0             |             | 500              | MHz       | AWG Nyquist limit                                      |  |  |  |  |  |

| Deviation gain                                               | 0             |             | 1.5              | Vp        |                                                        |  |  |  |  |  |

| Deviation gain resolution                                    |               | 14          |                  | Bits      | Limited by the output DAC                              |  |  |  |  |  |

|                                                              | Amplitude and | d offset mo | dulators (32-bit | modulatir | ng waveform)                                           |  |  |  |  |  |

| Deviation                                                    | -Dev. gain    |             | +Dev. gain       | Vp        |                                                        |  |  |  |  |  |

| Modulating signal resolution                                 |               | 16          |                  | Bits      | AWG waveform is truncated                              |  |  |  |  |  |

| Modulating signal BW                                         | 0             |             | 100              | MHz       | AWG Nyquist limit                                      |  |  |  |  |  |

| Deviation gain                                               | 0             |             | 1.5              | Vp        |                                                        |  |  |  |  |  |

| Deviation gain resolution                                    |               | 14          |                  | Bits      | Limited by the output DAC                              |  |  |  |  |  |

# IQ modulators specifications

| Devenuedor                     | M                           | 3202A-CH4 | 1        | Lin:to | C                                                      |  |  |  |  |

|--------------------------------|-----------------------------|-----------|----------|--------|--------------------------------------------------------|--|--|--|--|

| Parameter                      | Parameter Units Min Typ Max | Units     | Comments |        |                                                        |  |  |  |  |

| General specifications         |                             |           |          |        |                                                        |  |  |  |  |

| IQ modulators                  |                             | 4         |          |        | 1 per output channel                                   |  |  |  |  |

| Carrier signal source          |                             | FGs       |          |        | Refer to the FG specifications table in this document  |  |  |  |  |

| Modulating signal source       |                             | AWGs      |          |        | Refer to the AWG specifications table in this document |  |  |  |  |

| Amplitude deviation            | -1.5                        |           | 1.5      | Vp     |                                                        |  |  |  |  |

| Phase deviation                | -180                        |           | 180      | Deg    |                                                        |  |  |  |  |

| I modulating signal resolution |                             | 16        |          | Bits   | AWG waveform                                           |  |  |  |  |

| I modulating signal BW         | 0                           |           | 500      | MHz    | AWG Nyquist limit                                      |  |  |  |  |

| Q modulating signal resolution |                             | 16        |          | Bits   | AWG waveform                                           |  |  |  |  |

| Q modulating signal BW         | 0                           |           | 500      | MHz    | AWG Nyquist limit                                      |  |  |  |  |

# Clock system specifications

| Parameter              | M3202A-CH4 |     |     | Unite   | Commente |  |  |

|------------------------|------------|-----|-----|---------|----------|--|--|

| Farameter              | Min        | Тур | Max | – Units | Comments |  |  |

| General specifications |            |     |     |         |          |  |  |

| Clock frequency        |            | 1.0 |     | GHz     |          |  |  |

# AC performance

|                                    | M3202A-CH4                    |        |          |          |                                                                                                                                                        |  |  |

|------------------------------------|-------------------------------|--------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                          | Min                           | Тур    | Max      | Units    | Comments                                                                                                                                               |  |  |

| General characteristics            |                               |        |          |          |                                                                                                                                                        |  |  |

| Analog output jitter               |                               | < 2    |          | ps       | RMS (cycle-to-cycle)                                                                                                                                   |  |  |

| AWG trigger to output jitter       |                               | < 2    |          | ps       | RMS (cycle-to-cycle) for any trigger<br>referenced to the chassis clock;<br>independent of input trigger jitter if<br>input jitter < 4 ns peak-to-peak |  |  |

| Trigger resolution                 |                               | 10     |          | ns       |                                                                                                                                                        |  |  |

|                                    |                               | < 20   |          | ps       | Between ch 0 and ch 1, and ch 2 and ch 3                                                                                                               |  |  |

| Channel-to-channel skew            |                               | < 50   |          | ps       | Between any channel                                                                                                                                    |  |  |

|                                    |                               | < 150  |          | ps       | Between modules, chassis dependent <sup>2</sup>                                                                                                        |  |  |

| Clock output jitter                |                               | < 2    |          | ps       | RMS (cycle-to-cycle)                                                                                                                                   |  |  |

| Clock accuracy and stability       |                               | 100    |          | ppm      | PXIe, PXIe versions; chassis dependent <sup>1</sup>                                                                                                    |  |  |

|                                    |                               | AC     | characte | eristics |                                                                                                                                                        |  |  |

| Spurious-free dynamic range (SFDR) |                               |        |          |          | P <sub>out</sub> = 0 dBm, measured from DC to max frequency                                                                                            |  |  |

| • f <sub>out</sub> = 10 MHz        |                               | 68     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 40 MHz        |                               | 66     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 80 MHz        |                               | 62     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 120 MHz       |                               | 58     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 160 MHz       |                               | 54     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 200 MHz       |                               | 53     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 320 MHz       |                               | 55     |          | dBc      |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 390 MHz       |                               | 58     |          | dBc      |                                                                                                                                                        |  |  |

| Crosstalk (adjacent channels)      | Crosstalk (adjacent channels) |        |          |          |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 10 MHz        |                               | < -105 |          | dB       |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 40 MHz        |                               | -85    |          | dB       |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 80 MHz        |                               | -80    |          | dB       |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 120 MHz       |                               | -89    |          | dB       |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 160 MHz       |                               | -76    |          | dB       |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 200 MHz       |                               | -86    |          | dB       |                                                                                                                                                        |  |  |

| • f <sub>out</sub> = 320 MHz       |                               | -83    |          | dB       |                                                                                                                                                        |  |  |

| Devenator                         |     | M3202A-CH | 4   | 11     | Comments |  |  |

|-----------------------------------|-----|-----------|-----|--------|----------|--|--|

| Parameter                         | Min | Тур       | Max | Units  |          |  |  |

| Crosstalk (non-adjacent channels) |     |           |     |        |          |  |  |

| • f <sub>out</sub> = 10 MHz       |     | < -105    |     | dB     |          |  |  |

| • f <sub>out</sub> = 40 MHz       |     | -89       |     | dB     |          |  |  |

| • f <sub>out</sub> = 80 MHz       |     | -81       |     | dB     |          |  |  |

| • f <sub>out</sub> = 120 MHz      |     | -103      |     | dB     |          |  |  |

| • f <sub>out</sub> = 160 MHz      |     | -95       |     | dB     |          |  |  |

| • f <sub>out</sub> = 200 MHz      |     | -102      |     | dB     |          |  |  |

| • f <sub>out</sub> = 320 MHz      |     | -97       |     | dB     |          |  |  |

| AC characteristics                |     |           |     |        |          |  |  |

| Phase noise (SSB)                 |     |           |     |        |          |  |  |

| Offset = 1 kHz                    |     | < -127    |     | dBc/Hz |          |  |  |

| Offset = 10 kHz                   |     | < -133    |     | dBc/Hz |          |  |  |

| Offset = 100 kHz                  |     | < -138    |     | dBc/Hz |          |  |  |

| Average noise power density       |     | <         |     | dBm/Hz |          |  |  |

| Phase noise (SSB)                 |     |           |     |        |          |  |  |

| Offset = 1 kHz                    |     | < -127    |     | dBc/Hz |          |  |  |

1. This value corresponds to a chassis that fulfils the PXI Express specifications. This value can be improved with an external chassis clock or a System Timing Module.

2. This value corresponds to an M9005A PXIe chassis.

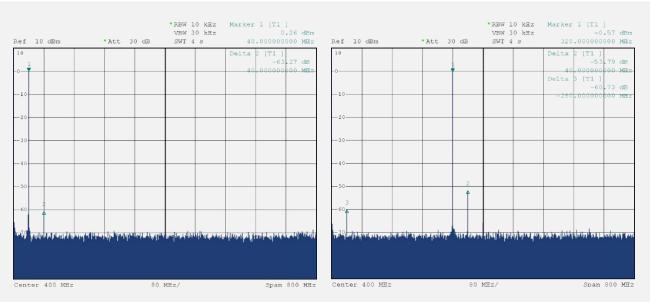

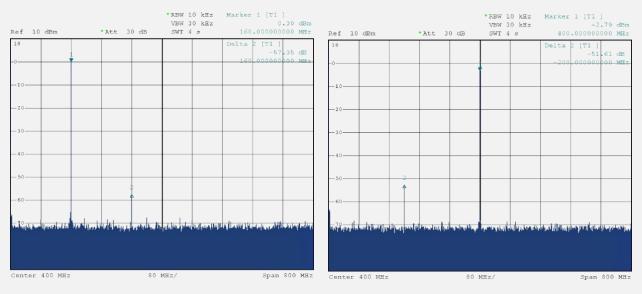

### AC performance, typical

Figure 2. Single-tone spectrum @  $f_{out} = 40 \text{ MHz}$

Figure 3. Single-tone spectrum @  $f_{out} = 160 \text{ MHz}$

Figure 4. Single-tone spectrum @  $f_{out} = 320 \text{ MHz}$

Figure 5. Single-tone spectrum @  $f_{out} = 400 \text{ MHz}$

# System Specifications

### Environmental specifications (PXI Express)

| Parameter               | M3202A-CH4  |       |      | Units    | Comments                                      |  |  |

|-------------------------|-------------|-------|------|----------|-----------------------------------------------|--|--|

| Faranieler              | Min Typ Max | Units |      |          |                                               |  |  |

| System bus              |             |       |      |          |                                               |  |  |

| Slots                   |             | 1     |      | Slot     | PXI Express (CompactPCI Express compatible)   |  |  |

| PCI Express type        |             | Gen 1 |      | _        | Chassis dependent                             |  |  |

| PCI Express link        | 1           |       | 4    | Lanes    | Automatic lane negotiation, chassis dependent |  |  |

| PCI Express speed       | 400         |       | 1600 | MBytes/s | Depends on # of lanes, chassis, congestion    |  |  |

| Power and temperature   |             |       |      |          |                                               |  |  |

| 3.3 V PXIe power supply |             | 1.5   |      | А        | ~ 5 W                                         |  |  |

| 12 V PXIe power supply  |             | 2     |      | А        | ~ 24 W                                        |  |  |

| Environmental <sup>1</sup>         |               |                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Temperature range                  | Operating     | 0 to +45 °C (10,000 feet)                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                    | Non-operating | -40 to +70 °C (up to 15,000 feet)                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| Max operative altitude             |               | 4000 m (10,000 feet)                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Operating Humidity range (%RH)     |               | 10 to 95% at 40 °C                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Non-operating Humidity range (%RH) |               | 5 to 95%                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| EMC                                |               | Complies with European EMC Directive <ul> <li>IEC/EN 61326-1</li> </ul>                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                    |               | <ul> <li>CISPR Pub 11 Group 1, class A</li> <li>This ISM device is in compliance with</li> <li>Canadian ICES-001.</li> <li>Cet appareil ISM est conforme à la norme</li> <li>NMB-001 du Canada.</li> <li>This ISM device is in compliance with</li> <li>Australian and New Zealand RCM.</li> <li>This ISM device is in compliance with South</li> <li>Korea EMC KCC.</li> </ul> |  |  |  |

Samples of this product have been type tested in accordance with the Keysight Environmental Test Manual and verified to be robust against the environmental stresses of Storage, Transportation and End-use; those stresses include but are not limited to temperature, humidity, shock, vibration, altitude and power line conditions. Test Methods are aligned with IEC 60068-2 and levels are similar to MIL-PRF-28800F Class 3.

# Learn more at: www.keysight.com

For more information on Keysight Technologies' products, applications, or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus